ADC 5 GSPS 14 bit

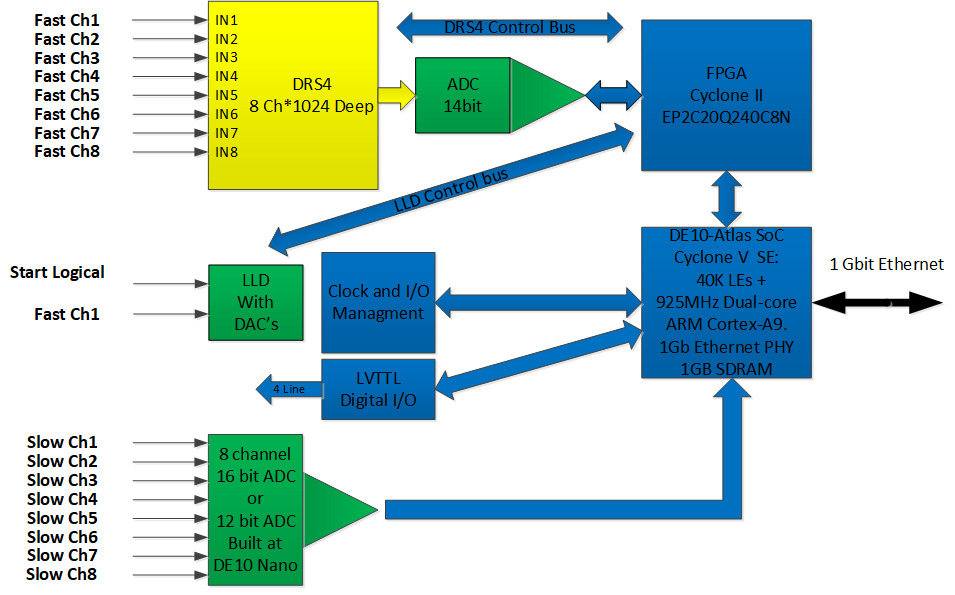

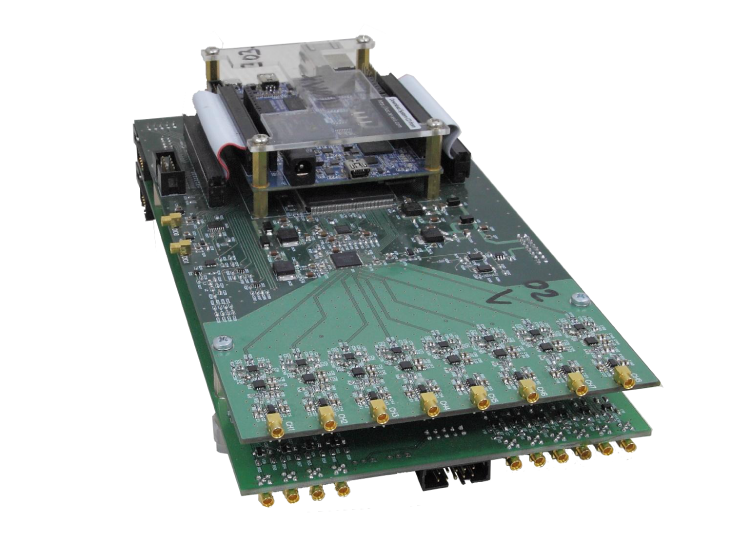

High speed 8-channel ADC based on DRS4 chip.

Features

- 8 50-Ohm terminated input channels with MMCХ connectors.

- Active input buffers which result in an analog bandwidth of 700 MHz (-3dB).

- High bandwidth analog switches disconnect inputs for internal voltage and time calibration.

- DRS4 chip, capable of sampling the 8 input signals simultaneously from 1.0 GSPS to 5 GSPS with 1024 sampling points each, software selectable.

- Software selectable choice quantity sampling point from 128 to 1024 for reducing dead time.

- 1.0 Vpp input dynamic range with adjustable DC offset.

- Adjustable post-trigger delay (up to 200 ns @ 5.0 GS/s).

- Readout rate is up to 3000 events per second with read 1024 sampling points in each 8 channels.

- Daisy chain capability (4 TTL I/O) with a MMCX connector.

- An external trigger input (2 TTL input) with a MMCX connector.

- Altera Cyclone® V SE 5CSEMA4U23C6N device (40k LA, 5k LAB).

- 925MHz Dual-core ARM Cortex-A9 processor.

- 1GB DDR3 SDRAM (32-bit data bus).

- 1 Gigabit Ethernet.

- 8 Channels 12bit ADC (up to 500KHz sampling) with a MMCX connector.

- SPI interface for auxiliary devices control (thermometers, etc).

- 24V/1A Power supply.

- LabBot-based firmware providing easy to use JSON/BSON-based API for all types of external control systems.

- Out-of-the-box web-based user interface for system debug and standalone usage.

Support & Service

- Device firmware might be adopted for specific use cases.

- It is possible to provide support for device integration in external control systems.

- Specific real-time online data processing capabilities can be added to the device firmware if needed.

- Specific external control system or diagnostic software can be developed on demand.

Application information

- High dynamic range (for accurate pulse characteristics measurement).

- High analog bandwidth and sampling rate.

- Significant on-board memory (to store thousands of scattered waveform records).

- High data throughput (for transferring the waveforms from all channels to a central processing unit in the time slot between consecutive triggers).

- An on-board FPGA (providing future-proof solution making possible calculations in real-time to achieve data reduction and therefore lower the data throughput requirements).